英伟达20年崛起之路:从游戏显卡到AI算力帝国的全面解析

作者:戈多Godot 来源:X,@GodotSancho

我们的故事,要从一个比赛说起。

李飞飞曾任 Google 副总裁及 Google Cloud AI/ML 首席科学家,同时也是斯坦福大学教授。但她还有另一重身份——ImageNet 大赛创办人。

ImageNet 大赛,正式名称 ILSVRC(ImageNet Large Scale Visual Recognition Challenge),是计算机视觉领域最具影响力的学术竞赛。

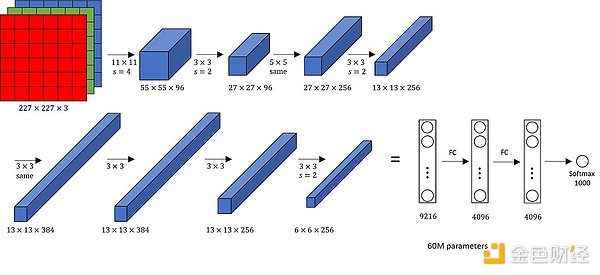

2012年 ImageNet 大赛,图灵奖得主杰弗里·欣顿(Geoffrey Hinton)的学生 Alex Krizhevsky,凭借 AlexNet 神经网络将图像识别错误率从 26% 降至 15.3%,以领先第二名 10.8个百分点的惊人优势震惊世界。

关键在于,AlexNet 并未使用超级计算机,而是仅靠两块普通的英伟达 GTX 580 游戏显卡完成训练。这是 AI 首次大规模使用 GPU 加速。在此之前,训练主要依赖 CPU。

这一结果等于向全世界宣告:AI 深度学习 + GPU = 算力革命。

当研究者们纷纷将目光转向 GPU 时,他们发现,只有英伟达的 CUDA 能让他们用类 C 语言编写复杂算法。

黄仁勋的“十年豪赌”

时间拨回 2006年。彼时 GPU 的职责只有一件事:渲染游戏画面。

但黄仁勋想让 GPU 变成通用计算工具。他坚信摩尔定律在 CPU 上已近失效,串行计算的未来必然是并行计算。

于是在 2006年,首席科学家 Ian Buck 领衔开发 CUDA(Compute Unified Device Architecture)。然而当时根本没人知道这东西有什么用。

为了支撑 CUDA,英伟达在每一颗 GPU 芯片中都额外嵌入一块专用计算电路。这意味着芯片面积增大、功耗升高、良品率下降、成本飙升。

除了极少数科研人员,没人买账。在深度学习爆发前,英伟达甚至主动向全球顶尖实验室免费寄送显卡,并派驻工程师协助优化。

CUDA 每年要烧掉英伟达约 5亿美元的研发费用,而当时英伟达一年的利润也不过几亿美元。2008年金融危机来袭,英伟达股价暴跌。

黄仁勋顶着股价暴跌的压力,坚持了整整十年。他始终坚信,GPU 不仅仅是用来渲染游戏画面的,而是一台通用并行处理器。

在 2012年那个转折点上,Intel 还在忙着维护 CPU 的霸权。Intel 长期迷信 CPU 的通用性,认为神经网络不过是一阵风。即便要算,也可以通过扩展 CPU 指令集(如 AVX)来解决。

AMD 当时正深陷收购后的阵痛,在软件投入上极其吝啬,导致其 AI 软件栈 ROCm 直到今天在易用性和稳定性上仍落后 CUDA 几个身位。

于是,2012年那个夏天,Alex Krizhevsky 面对 ImageNet 比赛中数百万张图片,正愁 CPU 算不动。他发现 CUDA 极其好用,便用类 C 语言写了几千行代码,跑在两块 GTX 580 上。

结果一出,全球学术界震动。原本要跑几周的实验,在 GPU 上几天便出了结果,且准确率断层领先。

放弃移动互联网,全面转向 GPU 计算

2013年,黄仁勋在 GTC 大会上做出了一个在当时看来近乎疯狂的决定,将公司重心全面转向 GPU 计算。

那是移动互联网的黄金时代,智能手机浪潮正盛。英伟达虽在手机市场受挫,却没有在手机芯片领域死磕,而是果断将资源全部抽调回来,押注当时还极为小众的数据中心加速计算。

同年,CUDA 进入 5.0/5.5 时代,引入动态并行(Dynamic Parallelism),GPU 可在不回传 CPU 的情况下自行启动新任务,大幅削减通信延迟。

与此同时,英伟达内部开始秘密研发 cuDNN,专为深度神经网络打造 CUDA 深度学习库,将神经网络中最难编写的卷积算法直接封装在底层库中。开发者只需调用一行命令即可完成操作。

而换到 AMD 的显卡上,同样的功能得自己写几百行复杂的底层代码。

2014年,深度学习框架混战拉开帷幕。Google 开源了 TensorFlow,英伟达随即派出大量工程师驻扎在开源社区,持续优化 CUDA 适配。当 TensorFlow 1.0 发布时,在英伟达显卡上的运行效率比 AMD 显卡高出数倍。

"显卡买英伟达",开始成为行业共识。

时至今日,CUDA 已从一个开发工具演变为一种行业标准语言。GitHub 上数以亿计的 AI 代码库依赖 CUDA 原语,大学课程几乎全部基于 CUDA 教学。这意味着新一代工程师在毕业前就已成为英伟达生态的"原住民"。

GitHub 上数以亿计的 AI 代码库依赖 CUDA 原语。大学课程几乎全基于 CUDA 教学。这意味着新一代的工程师在毕业前就已经成为了 NVIDIA 生态的“原住民”。

在 CUDA 之上,还有一套庞大的中间件与库体系。

A. cuDNN 与 cuBLAS

深度神经网络与线性代数库,历经十余年手工汇编级优化。

B. TensorRT

推理优化引擎,能自动融合算子、筛选最佳 kernel、执行量化校准。进入 Blackwell 时代后,TensorRT-LLM 更成为部署大语言模型的标配,直接支持 FP4/FP8 极致优化,竞争对手难以望其项背。

C. Triton Inference Server

已成为云原生 AI 推理的事实标准。

黄仁勋、马斯克 、OpenAI、《Attention is All You Need》…2017,AI 之神显灵

2017年,英伟达 Volta 架构诞生,旗舰产品 Tesla V100 随之发布。这颗芯片上第一次出现了 Tensor Core。

AI 计算从这一刻起,由矢量运算迈入矩阵运算时代。AI 算力爆发,迎来元年。

而早在 2016年底,黄仁勋便亲手将全球第一台搭载早期加速卡的 DGX-1 超级计算机,送到了当时还名不见经传的 OpenAI 办公室。

于是便有了那张著名的照片。照片中那个双手交叉的人,正是 OpenAI 出资人马斯克。这台机器后来成为训练 GPT 系列模型的"始祖机"。

2017年还发生了一件看似无关、实则决定了今天格局的大事:Google 发表论文《Attention is All You Need》,提出了 Transformer 架构。

这篇论文奠定了当今大语言模型的基石,彻底改变了 AI 处理信息的方式,并直接促成了后来 ChatGPT、Claude、Gemini 等大模型的诞生。

Transformer 架构的计算几乎全部由矩阵乘法构成,对算力的需求极为贪婪。

矩阵乘法,是不是有些眼熟?没错,英伟达的 Tensor Core,恰恰就是为矩阵乘法而生的。

至此,AI 的"寒武纪大爆发"正式拉开序幕。

宏观角度看,英伟达的霸主地位建立在三大支柱之上:

1)Tensor Core 架构

实现了矢量计算到矩阵计算的跨越、从通用计算到深度学习专用计算的跨越。

2)CUDA 软件生态

英伟达最深护城河,不仅是一门编程语言,更是一个涵盖 cuDNN、cuBLAS 等在内的庞大库与工具集合,使得迁移成本极高。

3)NVLink 互连技术

GPU 之间协作的桥梁。

通俗理解三者的关系:Tensor Core 是硬件创新,CUDA 是软件生态,NVLink 是互联通道,分别对应性能、生态与可组合性。

其中 Tensor Core 是英伟达真正甩开对手、确立 AI 霸主地位的关键。不理解 Tensor Core,就无法理解现代 AI 芯片。

Tensor Core 标志着 GPU 从图形渲染设备彻底转型为 AI 专用计算平台,以牺牲通用性为代价,换取矩阵乘法(Matrix Multiply)这一 AI 核心运算上的极致性能。

什么是 Tensor Core ?

Tensor Core 可进一步拆解为三个核心概念:

1)矩阵乘法(Matrix Multiplication) 2)混合精度(Mixed Precision) 3)架构演进

1)矩阵乘法(Matrix Multiplication)

从矢量计算迈向矩阵计算,是 Tensor Core 实现性能飞跃的核心逻辑。

传统 CUDA Core 执行的是标量或向量运算,例如 A + B。即便并发执行,每个周期也只能处理有限的数据点。

Tensor Core 则是嵌入 GPU 内部的 DSA(Domain Specific Architecture,领域专用架构)模块,相当于在通用 GPU 架构内部植入了 ASIC 级别的专用加速单元。

Tensor Core 并不是为了执行所有类型的指令,而是专攻一种特定运算——矩阵乘累加,即 D = A × B + C。

通俗地说,矢量计算像是一行一行地下达计算指令;矩阵计算则是直接输出一整块表格(4×4 矩阵)。

2)混合精度(Mixed Precision)——模糊的艺术

AI 的本质是概率,而非定论。

判断一张图里是猫还是狗,98.0001% 的概率与 98.0000000001% 的概率并无区别。但精度不同,对算力效率的影响却天差地别。

所谓混合精度,就是在不影响结果正确性的前提下,尽可能用低精度换取极致效率。

A. 如何衡量精度?

这里要引入一个概念:FP(Floating Point),即浮点数。

在计算机内部,任何数字都由 0 和 1(位/Bit)组成。一个浮点数通常包含三部分:

1)符号位(Sign),表示数字是正还是负。 2)指数位(Exponent),决定数字的大小范围。 3)尾数位(Mantissa/Fraction),决定数字精度,即小数点后有多少位。

常见的如 FP32,用 32位记录一个数,极其精确但占用空间大。

FP16 空间减半、速度翻倍,但精度和范围都随之缩小;FP4 则是极低精度,类似像素画,只能记录非常模糊的数值。

在计算机科学中,这本质上是在有效信息量(信息熵)、计算吞吐量与数值稳定性之间寻找最优解。

B. 混合精度如何运作?

a. 精度降级

计算时,Tensor Core 将原本 32位的输入强制转换为 16位。

FP32:1位符号 + 8位指数 + 23位尾数。 FP16:1位符号 + 5位指数 + 10位尾数。

尾数位从 23 降到 10,在矩阵乘法阶段,计算压力减少 4倍以上。

b. 累加保护

这是 Tensor Core 设计最精妙之处。

输入是 FP16,但累加使用 FP32——注意,加法用的是 FP32。

原因在于,小误差在相乘时尚且安全,但若在数万次相加中持续丢弃微小值,误差会迅速放大。通过在高精度下累加,英伟达保障了最终结果的精确性。

c. 损失缩放——对抗"下溢出"

AI 训练中,若全程使用 FP16,模型会崩溃。因为有些关键数据极其微小,FP16 根本无法表达,这个问题叫下溢出。

对策是,程序在计算前将损失值乘以一个巨大的系数(如 1024),强行将这些微小梯度推回 FP16 能表达的有效范围内。计算完成后,再除以 1024 还原。

C. 混合精度的极限——Microscaling Format(MX)微缩放

英伟达 V100 支持 FP16,到了 H100 变成 FP8,B200 进一步降至 FP4。

FP4 虽然比 FP16 快得更极致,但 FP4 只能表达 2⁴ = 16 个数值。要知道一张图片中的色号都远不止 16个,AI 将无法分辨梵高的《向日葵》和《星空》。

于是在 Blackwell 架构中,英伟达引入了 Microscaling Format,其核心思想是块浮点(Block Floating Point)。

通俗地说,AI 网络同一个向量块中,数值的数量级往往相近。与其对每个数值逐一缩放,不如按批处理:在一批数值中找到绝对值最大的那个,以此确定公共缩放因子。

最棘手的情况是,一组数据里混入了一个极大值,而其余都是极小值。

就像一张照片里既有太阳,旁边又有一只微弱的萤火虫。在 AI Transformer 的某些层中,这种"异常值"时常冒出。

这也正是英伟达在 Blackwell 架构中并未完全抛弃 FP8 和 FP16,并且在软件层面投入大量精力做平滑处理的原因。

3)架构演进

这里有个很方便的记忆方式:

Volta 是诞生——Ampere 走向主流——Hopper 大爆发——Blackwell 现在最火。

年份越往后,架构名越靠后,支持的精度(FP 后的数字)越小,矩阵运算的量级越大,AI 越像人。

2017年 Volta(V100):一场极其冒险的豪赌

2017年 Volta 问世,是英伟达发展历程中的关键分水岭。

在此之前 Pascal 架构,比如 GTX 1080 Ti,主要目标还是让游戏画面更好看。

而从 Volta 开始,黄仁勋做了一个当时看来极其冒险、事后证明是神来之笔的决定——模糊精度,即降低精度换取极致 AI 计算效率,让 GPU 从通用计算设备变成 AI 专用平台。

2017年之前,科学计算领域如天气模拟、核爆仿真,要求绝对精准,大家都在比拼 FP32 单精度甚至 FP64 双精度算力。

但突然之间,AI 爆发了。而 AI 网络恰恰很"抗噪"。

训练 AI 就像教小孩认猫,不需要告诉孩子这只猫耳朵长 3.1415926 厘米,只需要说大概 3 厘米就够了。

英伟达在 V100 上大力推行混合精度:计算用 FP16 半精度,累加时用 FP32 高精度防止误差积累。就像从写楷书变成写草书,速度瞬间翻倍,而 AI 准确率几乎没有下降。

这在当时极其冒险。在一颗极其昂贵的芯片上划出一大块面积,为一个当时仅有少数人在用的矩阵运算做专用电路,这是非常、非常、非常冒险的决定。

但黄仁勋和英伟达赌对了 AI 大爆发。

于是,这成为了其他竞争对手,如英特尔,至今落后的原因。

2018年 Turing(T4)——游戏画质的超级革新:光追与 DLSS

其实到此时,芯片的主要使用场景仍然是游戏画面渲染。

2018年,英伟达发布 Turing 架构(RTX 2080 Ti)。这是显卡历史上第一次将三种完全不同性质的处理器封装在同一块硅片上。

先解释一下背景。

在此之前,游戏画面渲染用的是光栅化(Rasterization),本质上就是 2D 贴图。老游戏玩家应该深有体会。比如水面倒影,其实是预先画好再贴上去的,玩家视角变了,影子纹丝不动。

光线追踪(Ray Tracing)则是模拟真实物理世界的光影效果。游戏中的光线和倒影会随玩家视角与光源实时变动。

光追在此之前并非做不了,只是计算量太大,游戏会直接卡成 PPT。

Turing 架构中,三种完全不同性质的处理器分别是 RT Core、CUDA Core 和 Tensor Core。

1)RT Core(Ray Tracing Core,光线追踪核心)

这是 Turing 的独创,专门负责计算光线与三角形的求交运算(BVH Traversal)。功能极其单一,只用于光追计算。将这类枯燥的几何运算从通用核心中抽离出来,效率提升了数十倍。

2)CUDA Core(通用计算核心)

继续承担传统的光栅化渲染任务。

3)Tensor Core(混合精度计算核心)

新增 INT8、INT4、INT1 支持,引入低精度推理能力,并首次将 Tensor Core 带入消费级显卡(RTX 20 系列)。

这里隐藏着一个伟大的发明——DLSS(深度学习超级采样)。

其逻辑是,光追计算太吃力,先渲染 1080P 画面,再用 Tensor Core 跑一个神经网络,将 1080P 的画面"脑补"成 4K。

这是 AI 生成内容在图形领域的首次大规模落地,证明了 AI 可以成为传统图形流水线的一部分。

2018年前后,传统性能增长已触及瓶颈。英伟达强推光追,本质上是重新定义了衡量显卡优劣的标准。AMD 或 Intel 即使想跟进,也缺乏像 Tensor Core 这样高效的硬件来支撑。

也就是说,英伟达形成了"算法 + 硬件 + 训练数据"的全方位封锁。

光追与 Tensor Core 的结合,还意外打开了通往元宇宙和数字孪生的大门。

既然 Tensor Core 能通过 AI 补全游戏画面,那能不能根据几张照片,直接"脑补"出一个真实的 3D 空间?这便是近几年大热的 NeRF 神经辐射场技术,实现了仅需几秒钟便能从视频生成 3D 模型。

2020年 Ampere(A100)——史上最成功的 AI 芯片

用"易用性革命"概括 A100,再合适不过。A100 之前,计算领域存在三个问题: 1)精度分裂。FP32 太慢,FP16 太难驾驭; 2)算力分裂。训练卡和推理卡互不通用; 3)资源分裂。大模型吃不饱,小模型吃撑了。

英伟达在 A100 上做出了堪称革命性的改进: 1)TF32(TensorFloat-32) 2)结构化稀疏(Structural Sparsity) 3)MIG(Multi-Instance GPU)

三者合力,实现了单张芯片的大一统。

TensorFloat-32 (TF32)

这是一个天才设计。还记得上文提到,此前 AI 计算沿用高精度方案,进行气象模拟、粒子仿真、核爆轨迹推演等场景吗?

TF32 能让那些习惯编写高精度 FP32 代码的开发者,不改代码,直接享受 Tensor Core 的模糊精度加速。

TF32 并非一种全新的存储格式,而是一种运算中间格式。

通过对 FP32 进行"截断"实现加速,本质是为了平衡计算精度与数值范围,设计的一种全新数学格式。

上篇提到,计算机内部任何数字都由 0 和 1(位/Bit)组成。一个浮点数通常由三部分构成: 1)符号位(Sign),数字是正还是负。 2)指数位(Exponent),决定数字的大小范围。 3)尾数位(Mantissa/Fraction),决定数字精度,即小数点后有多少位。

常见的如 FP32,用 32位记录一个数,极其精确但占用空间大;FP16 空间减半、速度翻倍,但精度和范围都随之缩小;FP4 则是极低精度,类似像素画,只能记录非常模糊的数值。

TF32 精妙之处在于,把 FP32 的范围和 FP16 的精度拼接在一起,形成一个 19位的格式:符号位 1 bit,指数位 8 bit(与 FP32 一致),尾数位 10 bit(与 FP16 一致)。

换句话说,TF32 是 FP32 与 FP16 之间的桥梁。是不是非常天才!!!!!!!

其工作流程如下:TF32 从显存中读取标准 FP32 数据,Tensor Core 在硬件电路中自动将尾数位从 23-bit 截断为 10-bit,转换为 TF32 格式,在此格式下执行高效乘法;所有中间乘积最终在 FP32 精度下完成累加;写回显存的数据依然是标准 FP32。

更关键的是,截断过程完全自动,意味着可以自动兜住数值的下溢出问题。

结构化稀疏(Structural Sparsity)

稀疏的本质,是把不重要的权重变成 0。就像识别一张猫的图片,大部分像素不起决定作用。

英伟达规定:在每 4 个连续权重中,必须有 2 个被设为 0。原本需要 64 bit 的数据,现在只需约 34 bit,模型在显存中几乎瘦身一半。

打个比方,如果显卡有 80GB 显存,原本只能装下 400亿参数(40B)的模型。开启结构化稀疏后,可能就能塞进一个接近 700亿(70B)甚至 800亿(80B)参数的模型。

而且性能还翻了倍。密集计算 156 TFLOPS(每秒 156 万亿次运算),稀疏计算 312 TFLOPS。

如果再叠加上文提到的 TF32 相较传统 FP32 带来的近 10倍提升,会发现 A100 在处理特定 AI 任务时,比几年前的旧显卡快了整整一个时代。

至于是否会担心连续 4 个权重都很重要、丢失关键信息?首先,模型尚未"定型"时,权重是可以流动调整的。

其次,神经网络具有极强的容错能力——虽然在某个小局部损失了信息,但其他层可以通过学习来弥补这一损失。

此外,稀疏并非随机删除,而是按权重大小裁剪。

MIG(Multi-Instance GPU)

MIG 用于芯片的空间管理,将单颗 GPU 在物理电路层面进行"硬分割"。没看错,是物理层面的切分。

在 A100 上,MIG 最多可将 GPU 切成 7 个独立实例(Instance),每一份都拥有自己专属的 Tensor Core 和显存路径。

切分方式灵活多样,比如切成 7 个小实例,或者 1 个大实例加 3 个小实例。硬件在出厂时就具备了这种"切割"能力,但具体怎么切、切成几份,完全可以在购入后通过软件命令实时控制。

在 A100 的硬件结构中,MIG 主要切割三类核心资源: 1)SM(流式多处理器)。计算核心,包含 CUDA Core 和 Tensor Core。 2)内存系统(Memory System),包括 HBM2 显存与 L2 缓存。 3)带宽(Pathways),芯片内部的数据传输通道(On-chip crossbar)。

每个实例拥有独立、固定的内存地址空间和计算路径。这意味着 A 实例在疯狂读写数据时,其产生的电磁信号和总线占用完全不会干扰到 B 实例。

这带来的好处显而易见:

-

其一,大幅提高利用率、节省成本。一张 A100 售价数万美元,如果只给一个博士生跑实验,未免太过奢侈。有了 MIG,一家公司可以让 7 位工程师在同一张卡上同时进行不同实验,效率提升 7倍。

-

其二,深受云租赁市场欢迎。云服务商可以按需灵活出租算力。

从更宏观的视角回望:

-

Volta(2017):证明通用计算的 CUDA Core 不再是唯一主角,矩阵计算的 Tensor Core 才是 AI 时代的皇冠。

-

Turing(2018):证明精度并非越高越好,低精度 INT8/INT4 才是推理时代的王道;同时证明 AI 可以反哺图形学。

-

Ampere(2020):证明分裂是低效的,统一才是最终答案。训练与推理被整合进同一块硅片(A100);同时证明稀疏化与 TF32 比"蛮力的精准"更具生产力。

在进入 2022年的 H100 之前,不得不先介绍英伟达垄断地位的另一项关键创新——NVLink。

如果说 Tensor Core 是芯片的心脏,那 NVLink 就是连接数万颗心脏的大动脉。

NVLink:GPU 之间的点对点高速互连协议

NVLink 是 GPU 之间的点对点高速互连协议,在 GPU 之间搭建高速公路,让 GPU 直接对话,绕过 CPU。

NVLink 存在的唯一目的——干掉 PCIe 瓶颈。

什么是 PCIe 瓶颈?

PCIe

免责声明:

1.资讯内容不构成投资建议,投资者应独立决策并自行承担风险

2.本文版权归属原作所有,仅代表作者本人观点,不代币币情的观点或立场

首页

首页 快讯

快讯